PCI Express

PCIe (Peripheral Component Interconnect Express), resmi disingkat sebagai PCIe, adalah standar serial kecepatan tinggi komputer expansion bus yang dirancang untuk menggantikan PCI tua, PCI-X, dan standar AGP bus. PCIe memiliki banyak perbaikan atas standar bus tersebut, termasuk Throughput sistem bus maksimum yang lebih tinggi, lebih rendah I / O jumlah pin dan jejak fisik lebih kecil, lebih baik kinerja-scaling untuk perangkat bus, deteksi kesalahan yang lebih rinci mekanisme dan pelaporan (Advanced Error Reporting (AER ),Dan fungsi hot-plug asli. Revisi lebih baru dari PCIe standar dukungan hardware I / O virtualisasi.

Antarmuka listrik PCIe juga digunakan dalam berbagai standar lainnya, terutama ExpressCard, antarmuka kartu ekspansi laptop.

Spesifikasi Format dipelihara dan dikembangkan oleh PCI-SIG (PCI Special Interest Group), sebuah kelompok lebih dari 900 perusahaan yang juga mempertahankan spesifikasi PCI konvensional. PCIe 3.0 adalah standar terbaru untuk kartu ekspansi yang ada di produksi dan tersedia pada komputer pribadi utama

Aplikasi

PCI Express beroperasi di konsumen, server dan aplikasi industri, sebagai Motherboard level interkoneksi (untuk menghubungkan Motherboard-mount peripheral), backplane interkoneksi pasif dan sebagai antarmuka kartu ekspansi untuk add-in papan.

Dalam hampir semua modern (pada 2012) PC, laptop dari konsumen dan desktop ke server data perusahaan, bus PCIe berfungsi sebagai interkoneksi motherboard-tingkat dasar, menghubungkan sistem host-prosesor dengan kedua terpadu peripheral (permukaan-mount IC) dan add-on peripheral (kartu ekspansi.) Dalam sebagian besar sistem ini, bus PCIe co-ada dengan satu atau lebih warisan PCI bus, untuk kompatibilitas dengan tubuh besar warisan PCI peripheral.

Arsitektur

onceptually, bus PCIe seperti pengganti serial kecepatan tinggi yang lebih tua PCI / PCI-X bus,

bus interkoneksi menggunakan shared alamat / data baris.

Perbedaan utama antara PCIe bus dan PCI tua adalah topologi bus. PCI menggunakan arsitektur bus paralel bersama, di mana tuan rumah PCI dan semua perangkat berbagi seperangkat alamat / data / kontrol garis. Sebaliknya, PCIe didasarkan pada topologi point-to-point, dengan link serial yang terpisah menghubungkan setiap perangkat ke kompleks akar (host). Karena topologi bus nya bersama, akses ke PCI bus lebih tua arbitrated (dalam kasus beberapa master), dan terbatas pada satu master pada suatu waktu, dalam satu arah. Selain itu, yang lebih tua PCI clocking skema membatasi jam bus ke paling lambat perifer di bus (terlepas dari perangkat yang terlibat dalam transaksi bus). Sebaliknya, link bus PCIe mendukung komunikasi full-duplex antara dua endpoint, dengan tidak ada pembatasan yang melekat pada akses bersamaan di beberapa endpoints.

Dalam hal protokol bus, PCIe komunikasi dirumuskan dalam paket. Pekerjaan data packetizing dan de-packetizing dan status pesan lalu lintas ditangani oleh lapisan transaksi port PCIe (dijelaskan kemudian). Radikal perbedaan sinyal listrik dan protokol bus memerlukan penggunaan faktor bentuk yang berbeda mekanik dan konektor ekspansi (dan dengan demikian, motherboard baru dan papan adaptor baru), slot PCI dan slot PCIe tidak saling dipertukarkan. Pada tingkat perangkat lunak, PCIe menjaga kompatibilitas dengan PCI; warisan perangkat lunak sistem PCI dapat mendeteksi dan mengkonfigurasi perangkat PCIe baru tanpa dukungan eksplisit untuk standar PCIe, meskipun fitur baru PCIe tidak dapat diakses.

PCIe link antara dua perangkat dapat terdiri dari mana saja 1-32 jalur. Dalam multi-link lane, paket data bergaris-garis di jalur, dan puncak skala data throughput yang dengan lebar keseluruhan link. Hitungan jalur secara otomatis dinegosiasikan selama inisialisasi perangkat, dan dapat dibatasi oleh salah satu endpoint. Misalnya, PCIe (× 1) kartu-jalur tunggal dapat dimasukkan ke dalam slot multi-lane (× 4, 8 ×, dll), dan siklus inisialisasi auto-menegosiasikan jumlah jalur saling mendukung tertinggi. Link dapat dinamis down-link mengkonfigurasi untuk menggunakan jalur yang lebih sedikit, sehingga memberikan beberapa ukuran toleransi kegagalan di hadapan jalur buruk atau tidak dapat diandalkan. Standar PCIe mendefinisikan slot dan konektor untuk beberapa lebar: × 1, × 4, 8 ×, × 16 × 32. Hal ini memungkinkan PCIe bus untuk melayani kedua aplikasi biaya-sensitif di mana throughput yang tinggi tidak diperlukan, serta aplikasi kinerja-kritis seperti grafis 3D, jaringan (10 Gigabit Ethernet, Gigabit Ethernet multiport), dan perusahaan penyimpanan (SAS, Fibre Channel. )

Sebagai titik acuan, perangkat PCI-X (133 MHz 64-bit) dan PCIe perangkat pada 4-jalur (× 4), Gen1 kecepatan memiliki kira-kira kecepatan transfer puncak yang sama dalam satu-arah: 1.064 MB / sec. Bus PCIe memiliki potensi untuk melakukan lebih baik daripada bus PCI-X dalam kasus di mana beberapa perangkat yang mentransfer data berkomunikasi secara bersamaan, atau jika komunikasi dengan PCIe perifer adalah dua arah.

Penghubung

Perangkat PCIe berkomunikasi melalui koneksi logis disebut link interconnector. Sebuah link adalah saluran komunikasi point-to-point antara dua port PCIe, yang memungkinkan baik untuk mengirim / menerima biasa PCI-permintaan (konfigurasi membaca / menulis, I / O membaca / menulis, memori baca / tulis) dan interupsi (INTx, MSI , MSI-X). Pada tingkat fisik, link terdiri dari 1 atau lebih jalur. kecepatan rendah periferal (seperti 802.11 Wi-Fi card) menggunakan jalur tunggal (× 1) link, sedangkan adapter grafis biasanya menggunakan lebih luas (dan dengan demikian, lebih cepat) Link 16-lane.

Jalur

Jalur A terdiri dari dua pasang diferensial sinyal: satu pasang untuk menerima data, yang lain untuk transmisi. Dengan demikian, masing-masing jalur terdiri dari empat kabel atau sinyal jejak. Secara konseptual, masing-masing jalur digunakan sebagai aliran byte full-duplex, mengangkut paket data dalam format delapan-bit 'byte', antara endpoint dari link, di kedua arah secara bersamaan [6] Fisik slot PCIe mungkin berisi 1-30-. dua jalur, dalam kekuatan dari dua (1, 2, 4, 8, 16 dan 32) jumlah Lane ditulis dengan awalan × (misalnya, × 16 merupakan kartu enam belas jalur atau Slot), dengan × 16 menjadi ukuran terbesar umum dipakai

Serial bus

The berikat serial format dipilih lebih tradisional Format bus paralel karena keterbatasan yang terakhir, termasuk operasi tunggal-duplex, jumlah sinyal kelebihan dan bandwidth inheren lebih rendah karena waktu miring. Timing miring hasil dari sinyal-sinyal listrik yang terpisah dalam antarmuka paralel bepergian ke konduktor yang berbeda-panjang, pada potensi yang berbeda sirkuit lapisan papan tercetak, dengan kecepatan sinyal yang mungkin berbeda. Meskipun ditransmisikan secara bersamaan sebagai satu kata, sinyal pada antarmuka paralel pengalaman waktu perjalanan yang berbeda dan tiba di tujuan mereka pada saat-saat yang berbeda. Ketika clock rate antarmuka meningkat ke titik di mana kebalikannya (yaitu, periode clock) lebih pendek dari yang mungkin waktu terbesar antara kedatangan sinyal, sinyal tidak lagi datang dengan kebetulan cukup untuk membuat pemulihan dari kata ditransmisikan mungkin. Karena waktu miring atas bus paralel dapat berjumlah beberapa nanodetik, keterbatasan bandwidth yang dihasilkan dalam kisaran ratusan megahertz.

Sebuah antarmuka serial tidak menunjukkan waktu miring karena hanya ada satu sinyal diferensial di setiap arah dalam setiap jalur, dan tidak ada sinyal clock eksternal karena informasi clocking tertanam dalam sinyal serial. Dengan demikian, keterbatasan bandwidth yang khas pada sinyal serial dalam kisaran multi-gigahertz. PCIe hanyalah satu contoh dari kecenderungan umum dari bus paralel ke serial interkoneksi. Contoh lain termasuk Serial ATA, USB, SAS, FireWire (1394) dan RapidIO.

Desain serial Multichannel meningkatkan fleksibilitas dengan mengalokasikan perangkat lambat untuk jalur kurang dari perangkat cepat.

Faktor bentuk

PCI Express (standard)

Sebuah kartu PCIe cocok menjadi slot ukuran fisik atau lebih besar (maksimum × 16), tetapi tidak masuk ke dalam slot PCIe lebih kecil (misalnya, × 16 kartu dalam × 8 Slot). Beberapa slot menggunakan soket terbuka untuk mengizinkan kartu fisik lagi dan menegosiasikan sambungan listrik terbaik yang tersedia. Jumlah jalur sebenarnya terhubung ke slot mungkin juga kurang dari jumlah didukung oleh ukuran slot fisik.

Contohnya adalah × 8 Slot yang sebenarnya hanya berjalan pada × 1. Slot ini memungkinkan setiap × 1, × 2, × 4 atau 8 × kartu, meskipun hanya berjalan pada kecepatan × 1. Jenis socket disebut × 8 (× 1 mode) Slot, berarti secara fisik menerima hingga × 8 kartu tetapi hanya berjalan pada kecepatan × 1. Hal ini juga kadang-kadang ditetapkan sebagai "× Ukuran (@ × kapasitas)" (misalnya, "× 16 (@ × 8)"). Keuntungannya adalah bahwa hal itu dapat menampung kisaran yang lebih besar dari kartu PCIe tanpa membutuhkan hardware motherboard untuk mendukung kecepatan transfer penuh. Hal ini membuat desain dan biaya implementasi bawah.

Pinout

Di tabel berikut mengidentifikasi konduktor pada setiap sisi konektor tepi pada kartu PCI Express. Sisi solder dari printed circuit board (PCB) adalah sisi A, dan sisi komponen adalah B side.PRSNT1 # dan PRSNT2 # pin harus sedikit lebih pendek daripada yang lain, untuk memastikan bahwa kartu hot-terpasang sepenuhnya dimasukkan . The WAKE # pin menggunakan tegangan penuh untuk membangunkan komputer, tetapi harus ditarik tinggi dari daya siaga untuk menunjukkan bahwa kartu tersebut mampu bangun.

Daya (Power)

Semua ukuran × 4 dan 8 × kartu PCI Express diperbolehkan konsumsi daya maksimum 25 W. Semua × 1 kartu yang awalnya 10 W, kartu tinggi penuh dapat mengkonfigurasi dirinya sendiri sebagai 'daya tinggi' mencapai 25 W, sementara setengah -height × 1 kartu adalah tetap pada 10 W. Semua ukuran × 16 kartu yang awalnya 25 W, seperti × 1 kartu, kartu setengah tinggi terbatas ke nomor ini sementara kartu tinggi penuh dapat meningkatkan kekuatan mereka setelah konfigurasi. Mereka dapat menggunakan hingga 75 W (3,3 V / 3 A + 12 V/5.5 A), meskipun spesifikasi menuntut bahwa konfigurasi yang lebih tinggi-daya digunakan untuk kartu grafis saja, sedangkan kartu tujuan lainnya adalah untuk tetap pada 25 konektor WOptional tambahkan 75 W (6-pin) dan / atau 150 W (8-pin) daya hingga 525 W total (75 W + 3 × 150 W).

Kartu Mini PCI Express (Mini card PCIe)

Kartu Mini PCI Express (juga dikenal sebagai Mini PCI Express, Mini PCIe, dan Mini PCI-E) adalah pengganti untuk Mini PCI form factor, berdasarkan PCI Express. Hal ini dikembangkan oleh PCI-SIG. Perangkat host mendukung PCI Express dan USB 2.0, dan setiap kartu dapat menggunakan salah satu standar. Sebagian besar komputer laptop dibangun setelah 2005 didasarkan pada PCI Express dan dapat memiliki beberapa slot Kartu Mini.

Dimensi fisik

Mini PCI Express Card adalah 30 × 50,95 mm. Ada konektor tepi 52-pin, yang terdiri dari dua baris terhuyung-huyung pada 0,8 mm pitch. Setiap baris memiliki delapan kontak, kesenjangan setara dengan empat kontak, kemudian lebih lanjut 18 kontak. Kartu setengah-panjang juga ditentukan 30 × 26,8 mm. Kartu memiliki ketebalan 1,0 mm (tidak termasuk komponen).

listrik Interface

Mini PCI Express konektor tepi Card menyediakan beberapa koneksi dan bus:

PCIe × 1

USB 2.0

SMBus

Kabel untuk diagnostik LED untuk jaringan nirkabel (yaitu, Wi-Fi) status pada chassis komputer

Kartu SIM untuk aplikasi GSM dan WCDMA. (Sinyal UIM di spec)

Perpanjangan masa depan untuk lain PCIe lane

1,5 dan 3,3 volt

Mini PCI Express & mSATA

Meskipun berbagi mini-PCI Express faktor bentuk, slot mSATA belum tentu elektrik kompatibel dengan Mini PCI Express. Untuk alasan ini, hanya notebook tertentu yang kompatibel dengan mSATA drive. Kebanyakan sistem kompatibel didasarkan pada arsitektur prosesor Intel Sandy Bridge, menggunakan platform Huron River. Tapi untuk konektor mSATA / mini-PCI-E, satu-satunya prasyarat adalah bahwa ada sebuah saklar yang membuatnya baik mSATA atau slot mini PCI-E dan dapat diimplementasikan pada platform apapun.

Notebook Lenovo seperti T-Series, W-Series, dan X-Series ThinkPad dirilis pada bulan Maret-April 2011 memiliki dukungan untuk kartu SSD mSATA dalam slot kartu WWAN mereka. The ThinkPad Edge E220s/E420s, dan Lenovo IdeaPad Y460/Y560 juga mendukung mSATA

Beberapa notebook (terutama Asus Eee PC, Apple MacBook Air, dan Dell mini9 dan mini10) menggunakan varian dari Kartu Mini PCI Express sebagai SSD. Varian ini menggunakan pin non-reserved pendiam dan beberapa untuk melaksanakan SATA dan IDE antarmuka passthrough, hanya menjaga USB, garis tanah, dan kadang-kadang inti PCIe 1x bus utuh. [14] Hal ini membuat flash 'miniPCIe' dan solid state drive dijual untuk netbook sebagian besar tidak sesuai dengan benar Mini PCI Express implementasi.

Juga, khas Asus miniPCIe SSD adalah 71 mm panjang, menyebabkan mm Model Dell 51 sampai sering menjadi (salah) disebut sebagai setengah panjang. Benar 51 mm Mini PCIe SSD diumumkan pada tahun 2009, dengan dua ditumpuk PCB lapisan, yang memungkinkan untuk kapasitas penyimpanan yang lebih tinggi. Mengumumkan desain mempertahankan antarmuka PCIe, sehingga kompatibel dengan standar Mini slot PCIe. Tidak ada produk kerja yang belum dikembangkan.

Intel Desktop Board memiliki banyak dengan PCIe × 1 slot Mini-Card yang biasanya tidak mendukung mSATA SSD. Daftar Dewan Desktop yang native mendukung mSATA di PCIe x1 slot Mini-Card (biasanya multiplexing dengan port SATA) disediakan pada situs Dukungan Intel

PCI Express Eksternal Kabel

PCI Express Eksternal Kabel (juga dikenal sebagai Eksternal PCI Express, kabel PCI Express, atau ePCIe) spesifikasi yang dirilis oleh PCI-SIG pada Februari 2007. Kabel dan konektor standar telah ditetapkan untuk × 1, × 4, 8 ×, dan 16 × lebar link, dengan transfer rate 250 MB / s per jalur. PCI-SIG juga mengharapkan norma akan berkembang mencapai 500 MB / s, seperti dalam PCI Express 2.0. Panjang kabel maksimum tetap belum ditentukan. Sebuah contoh dari penggunaan kabel PCI Express adalah kandang logam, yang mengandung sejumlah slot PCI dan sirkuit adapter PCI-to-ePCIe. Perangkat ini tidak akan mungkin kalau bukan untuk spec ePCIe.

Bentuk derivatif

Ada beberapa jenis kartu ekspansi lain yang berasal dari PCIe. Ini termasuk:

Low height card

ExpressCard: penerus faktor bentuk PC Card (dengan × 1 PCIe dan USB 2.0, hot-pluggable)

PCI Express ExpressModule: faktor bentuk modular hot-pluggable yang ditetapkan untuk server dan workstation

Kartu XQD: a berbasis PCI Express kartu flash standar oleh Asosiasi CompactFlash

XMC: mirip dengan CMC / PMC form factor (VITA 42.3)

AdvancedTCA: pelengkap CompactPCI untuk aplikasi yang lebih besar, mendukung topologi backplane berbasis seri

AMC: pelengkap spesifikasi AdvancedTCA, mendukung prosesor dan I / O modul pada ATCA papan (× 1, × 2, × 4 atau 8 × PCIe).

FeaturePak: format kecil kartu ekspansi (43 × 65 mm) untuk embedded dan aplikasi faktor bentuk kecil, melainkan mengimplementasikan dua × 1 PCIe link pada konektor kepadatan tinggi bersama dengan USB, I2C, dan hingga 100 poin dari I / O.

Universal IO: Sebuah varian dari Super Micro Computer Inc dirancang untuk digunakan dalam rak low profile mount chassis. Ini telah braket konektor terbalik sehingga tidak dapat disimpan dalam sebuah PCI Express soket normal, tapi pin yang kompatibel dan dapat dimasukkan jika braket akan dihapus.

Thunderbolt: Sebuah varian dari Intel dan Apple yang menggabungkan DisplayPort dan protokol PCIe dalam faktor bentuk yang kompatibel dengan Mini DisplayPort.

Serial Digital Video Out: beberapa 9xx series chipset Intel memungkinkan untuk menambahkan output tambahan untuk video terintegrasi ke slot PCIe (kebanyakan berdedikasi dan 16 jalur)

Sementara dalam pengembangan awal, PCIe awalnya disebut sebagai HSI (High Speed untuk interkoneksi), dan mengalami perubahan nama menjadi 3GIO (untuk 3rd Generation I / O) sebelum akhirnya menetap di perusahaan nama PCI-SIG PCI Express. Ini pertama kali disusun oleh kelompok kerja teknis yang bernama Arapaho Work Group (AWG) bahwa, untuk konsep awal, hanya terdiri dari insinyur Intel. Selanjutnya AWG diperluas untuk mencakup mitra industri.

PCIe adalah teknologi dalam pembangunan konstan dan perbaikan. PCI ekspres implementasi saat ini adalah versi 3.0.

PCI Express 1.0a

Pada tahun 2003, PCI-SIG memperkenalkan PCIe 1.0a, dengan per-jalur data rate 250 MB / s dan kecepatan transfer 2,5 gigatransfers per detik (GT / s). Transfer rate dinyatakan dalam transfer per detik bukan bit per detik karena jumlah transfer termasuk bit overhead, yang tidak memberikan throughput tambahan.

PCIe 1.x menggunakan skema encoding 8B/10B yang menghasilkan 20 persen ((10-8) / 10) overhead pada tingkat bit mentah. Ini menggunakan clock rate 2,5 GHz, sehingga memberikan efektif 250 000 000 byte per detik (250 MB / s) data rate maksimum.

PCI Express 1.1

Pada tahun 2005, PCI-SIG diperkenalkan PCIe 1.1. Spesifikasi ini diperbarui termasuk klarifikasi dan beberapa perbaikan, tetapi sepenuhnya kompatibel dengan PCI Express 1.0a. Tidak ada perubahan yang dilakukan pada data rate.

PCI Express 2.0

PCI-SIG mengumumkan ketersediaan PCI Express 2.0 Basis spesifikasi pada 15 Januari 2007

2,0 standar PCIe menggandakan kecepatan transfer dibandingkan dengan PCIe 1,0-5 GT / s dan throughput per-jalur naik dari 250 MB / s hingga 500 MB / s. Ini berarti 32-lane konektor PCIe (× 32) dapat mendukung throughput hingga 16 GB / s agregat.

PCIe 2.0 slot motherboard sepenuhnya kompatibel dengan PCIe kartu v1.x. PCIe 2.0 kartu juga umumnya kompatibel dengan motherboard PCIe 1.x, menggunakan bandwidth PCI Express 1.1. Secara keseluruhan, kartu grafis atau motherboard dirancang untuk v2.0 akan bekerja dengan v1.1 yang lain atau 1.0a.

PCI-SIG juga mengatakan bahwa PCIe 2.0 memiliki fitur perbaikan data point-to-point protokol transfer dan arsitektur perangkat lunak.

Pertama PCIe 2.0 chipset mampu Intel adalah X38 dan papan mulai kapal dari berbagai vendor (Abit, Asus, Gigabyte) pada tanggal 21 Oktober, 2007AMD mulai mendukung PCIe 2.0 dengan AMD 700 series chipset dan nVidia dimulai dengan MCP72All chipset sebelum Intel , termasuk chipset Intel P35, didukung PCIe 1.1 atau 1.x 1.0aLike, PCIe 2.0 menggunakan skema encoding 8B/10B, sehingga memberikan, per jalur, sebuah 4 Gbit / s max transfer rate efektif dari yang 5 GT / s baku data rate.

PCI Express 2.1

PCI Express 2.1 mendukung sebagian besar dari manajemen, dukungan, dan sistem pemecahan masalah direncanakan untuk implementasi penuh pada PCI Express 3.0. Namun, kecepatan adalah sama dengan PCI Express 2.0.

PCI Express 3.0

PCI Express 3.0 Basis spesifikasi revisi 3.0 dibuat tersedia pada November 2010, setelah beberapa penundaan. Pada bulan Agustus 2007, PCI-SIG mengumumkan bahwa PCI Express 3.0 akan membawa bit rate dari 8 gigatransfers per detik (GT / s), dan bahwa hal itu akan kompatibel dengan implementasi PCIe yang ada. Pada saat itu, ia juga mengumumkan bahwa spesifikasi final untuk PCI Express 3.0 akan ditunda sampai 2011

Fitur baru untuk spesifikasi PCIe 3.0 termasuk sejumlah optimasi untuk meningkatkan sinyal dan integritas data, termasuk pemancar dan penerima pemerataan, peningkatan PLL, jam pemulihan data, dan perangkat tambahan saluran untuk saat ini didukung topologi.

Setelah analisis teknis enam bulan kelayakan skala bandwidth interkoneksi PCIe, analisis PCI-SIG menemukan bahwa 8 gigatransfers per detik dapat diproduksi dalam arus utama teknologi proses silikon, dan dapat digunakan dengan bahan murah yang ada dan infrastruktur, sambil mempertahankan kompatibilitas penuh (dengan dampak yang dapat diabaikan) ke PCIe stack protokol.

PCIe 3.0 upgrade skema pengkodean untuk 128b/130b dari 8b/10b sebelumnya, mengurangi biaya overhead menjadi sekitar 1,54% ((130-128) / 130), yang bertentangan dengan 20% dari PCIe 2.0. Hal ini dicapai dengan teknik yang disebut "scrambling" yang berlaku biner polinomial yang dikenal dengan aliran data dalam topologi umpan balik. Karena jumlahnya banyak berebut diketahui, data dapat dipulihkan dengan menjalankan melalui topologi umpan balik menggunakan polinomial terbalik

PCIe 3.0 's 8 tingkat GT / s bit efektif memberikan 985 MB / s per jalur, ganda PCIe 2.0 bandwidth. PCI-SIG mengharapkan PCIe 3.0 spesifikasi untuk menjalani pemeriksaan teknis yang ketat dan validasi sebelum dirilis ke industri. Proses ini, yang diikuti dalam pengembangan generasi sebelumnya Basis PCIe dan faktor bentuk berbagai spesifikasi, termasuk bukti yang menguatkan parameter listrik akhir dengan data yang berasal dari silikon tes dan simulasi lainnya yang dilakukan oleh beberapa anggota PCI-SIG.

Pada tanggal 18 November 2010, PCI Special Interest Group secara resmi menerbitkan diselesaikan PCI Express 3.0 spesifikasi kepada para anggotanya untuk membangun perangkat berdasarkan versi baru PCI Express.

Kartu AMD andalan terbaru grafis, Radeon HD 7970, diluncurkan pada tanggal 9 Januari 2012, pertama PCIe 3.0 kartu grafis dunia. ulasan awal menunjukkan bahwa antarmuka baru tidak akan meningkatkan kinerja grafis dibandingkan dengan sebelumnya PCIe 2.0, yang pada saat penulisan, masih kurang dimanfaatkan. Namun, antarmuka baru akan terbukti menguntungkan bila digunakan untuk tujuan umum komputasi dengan teknologi seperti OpenCL, CUDA, dan C + + AMP.

PCI Express 4.0

Pada tanggal 29 November 2011, PCI-SIG mengumumkan PCI Express 4.0 menampilkan 16 GT / s, masih didasarkan pada teknologi tembaga. Selain itu, aktif dan siaga optimasi Daya untuk diselidiki. Spesifikasi final diharapkan akan dirilis pada 2014-15

Status saat ini

Pada 2013 PCI Express telah menggantikan AGP sebagai antarmuka default untuk kartu grafis pada sistem baru. Hampir semua model kartu grafis dirilis sejak 2010 oleh AMD (ATI) dan NVIDIA menggunakan PCI Express. NVIDIA menggunakan transfer data bandwidth tinggi dari PCIe untuk perusahaan Scalable Link Interface (SLI) teknologi, yang memungkinkan beberapa kartu grafis dari chipset yang sama dan nomor model untuk berjalan secara bersamaan, yang memungkinkan peningkatan kinerja. AMD juga telah mengembangkan sistem multi-GPU berdasarkan PCIe disebut CrossFire. AMD dan NVIDIA telah merilis chipset motherboard yang mendukung sebanyak empat PCIe × 16 slot, yang memungkinkan konfigurasi kartu tri-GPU dan quad-GPU.

Ekstensi dan arah masa depan

Beberapa vendor menawarkan PCIe atas produk serat, tetapi ini umumnya menemukan gunakan hanya dalam kasus-kasus tertentu di mana PCIe transparan bridging adalah lebih baik untuk menggunakan standar yang lebih utama (seperti Infiniband atau Ethernet) yang mungkin memerlukan perangkat lunak tambahan untuk mendukungnya , implementasi saat ini fokus pada jarak daripada bandwidth mentah dan biasanya tidak menerapkan link penuh × 16.

Aplikasi pusat data tertentu (seperti cluster komputer besar) memerlukan penggunaan serat optik interkoneksi karena jarak dan keterbatasan latency yang melekat dalam kabel tembaga. Biasanya, standar-berorientasi jaringan seperti Ethernet atau Fibre Channel sudah cukup untuk aplikasi ini, tetapi dalam beberapa kasus

overhead diperkenalkan oleh protokol routable tidak diinginkan dan interkoneksi-tingkat yang lebih rendah, seperti InfiniBand, RapidIO, atau NUMAlink diperlukan. Standar lokal-bus seperti PCIe dan HyperTransport secara prinsip dapat digunakan untuk tujuan ini

namun pada 2012 ada vendor besar menawarkan sistem di pembuluh darah ini.

Thunderbolt dikembangkan oleh Intel sebagai antarmuka kecepatan tinggi untuk keperluan umum menggabungkan × 4 PCIe link dengan DisplayPort dan pada awalnya dimaksudkan untuk menjadi sebuah antarmuka serat semua, namun karena kesulitan awal dalam menciptakan serat interkoneksi ramah konsumen, implementasi yang paling awal adalah sistem-serat tembaga hibrida. Sebuah pengecualian, Sony VAIO Z VPC-Z2, menggunakan port USB tidak standar dengan komponen optik untuk menghubungkan ke layar adaptor PCIe tempel. Apple telah menjadi pendorong utama adopsi Thunderbolt sampai 2011, meskipun beberapa vendor lainnya

telah mengumumkan produk baru dan sistem menampilkan Thunderbolt.

Hardware ringkasan protokol

Link PCIe dibangun di sekitar pasangan searah berdedikasi serial (1-bit), koneksi point-to-point yang dikenal sebagai jalur. Hal ini kontras dengan koneksi PCI sebelumnya, yang merupakan sistem berbasis bus di mana semua perangkat berbagi sama bidirectional, 32-bit atau 64-bit paralel bus.

PCI Express adalah protokol berlapis, terdiri dari lapisan transaksi, lapisan data link, dan lapisan fisik. Data Link Layer dibagi untuk menyertakan kontrol akses (MAC) sublapisan media. Physical Layer dibagi menjadi sub-lapisan logis dan listrik. Fisik logis-sublayer berisi sublayer coding fisik (PCS). Istilah ini dipinjam dari IEEE 802 jaringan Model protokol.

Physical Layer

PCIe Physical Layer (PHY, PCIEPHY, PCI Express PHY, atau PCIe PHY) spesifikasi dibagi menjadi dua sub-lapisan, sesuai dengan spesifikasi listrik dan logis. Logis sublayer yang kadang-kadang lebih dibagi menjadi sublayer MAC dan PCS, walaupun pembagian ini tidak secara resmi bagian dari spesifikasi PCIe. Sebuah spesifikasi diterbitkan oleh Intel, Interface PHY untuk PCI Express (PIPA), mendefinisikan MAC / PCS partisi fungsional dan antarmuka antara dua sub-lapisan. Opium spesifikasi juga mengidentifikasi media lampiran (PMA) lapisan fisik, yang meliputi serializer / deserializer (SerDes) dan sirkuit analog lainnya, namun sejak SerDes implementasi sangat bervariasi antara vendor ASIC, PIPA tidak menentukan sebuah antarmuka antara PCS dan PMA .

Pada tingkat listrik, masing-masing terdiri dari dua jalur unidirectional LVDS atau PCML pasang di 2,525 Gbit / s. Mengirim dan menerima pasangan tersebut terpisah diferensial, untuk total empat kabel data yang per lajur.

Koneksi antara dua perangkat PCIe dikenal sebagai link, dan dibangun dari koleksi satu atau lebih jalur. Semua perangkat harus mendukung minimal satu jalur (× 1) link. Perangkat mungkin opsional link dukungan yang lebih luas terdiri dari 2, 4, 8, 12, 16, atau 32 jalur. Hal ini memungkinkan untuk kompatibilitas sangat baik dalam dua cara:

Sebuah kartu PCIe fisik cocok (dan bekerja dengan benar) pada slot yang setidaknya sebagai besar seperti itu (misalnya, kartu × 1 berukuran akan bekerja dalam ukuran slot);

Sebuah slot ukuran fisik yang besar (misalnya, × 16) dapat kabel elektrik dengan jalur sedikit (misalnya, × 1, × 4, 8 ×, atau 12 ×) asalkan menyediakan koneksi tanah yang dibutuhkan oleh slot fisik yang lebih besar ukuran.

Dalam kedua kasus, PCIe menegosiasikan tertinggi saling mendukung jumlah jalur. Banyak kartu grafis, motherboard dan versi bios diverifikasi untuk mendukung × 1, × 4, 8 × 16 × dan konektivitas pada koneksi yang sama.

Meskipun kedua akan sinyal-kompatibel, biasanya tidak mungkin untuk menempatkan kartu PCIe fisik lebih besar (misalnya, kartu × 16 ukuran) menjadi lebih kecil slot meskipun jika slot PCIe yang diubah atau riser yang digunakan kebanyakan motherboard akan membiarkan ini. Biasanya teknik ini digunakan untuk menampilkan ke beberapa monitor dalam konfigurasi simulator.

Lebar konektor PCIe adalah 8,8 mm, sedangkan tinggi adalah 11,25 mm, dan panjang adalah variabel. Bagian tetap konektor adalah 11,65 mm dan panjang berisi dua baris 11 (22 pin total), sedangkan panjang bagian lainnya adalah variabel tergantung pada jumlah jalur. Pin yang berjarak pada interval 1 mm, dan ketebalan kartu masuk ke konektor 1.8 mm

Transmisi data

PCIe mengirim semua pesan kontrol, termasuk interupsi, di link yang sama digunakan untuk data. Protokol serial yang tidak pernah akan diblokir, jadi latency masih sebanding dengan PCI konvensional, yang telah memotong jalur khusus.

Data yang ditransmisikan pada link beberapa jalur yang interleaved, yang berarti bahwa setiap byte diturunkan berturut-turut Lanes. Spesifikasi PCIe mengacu interleaving ini sebagai data striping. Sementara memerlukan kompleksitas hardware signifikan untuk menyinkronkan (atau deskew) yang masuk belang data, striping signifikan dapat mengurangi latency dari byte n pada link. Karena padding persyaratan, striping mungkin tidak selalu mengurangi latency paket data kecil pada link.

Seperti dengan data rate protokol transmisi serial tinggi lainnya, jam tertanam dalam sinyal. Pada tingkat fisik, PCI Express 2.0 menggunakan skema encoding 8B/10B

untuk memastikan bahwa string yang berturut-turut atau nol berturut-turut dibatasi panjangnya. Coding ini digunakan untuk mencegah penerima dari kehilangan melacak di mana tepi bit. Dalam skema pengkodean setiap delapan (uncoded) payload bit data akan diganti dengan 10 (encoded) bit dari data, menyebabkan 20% overhead listrik di bandwidth. Untuk meningkatkan bandwidth yang tersedia, PCI Express versi 3.0 menggunakan pengkodean 128b/130b gantinya: serupa tapi dengan overhead jauh lebih rendah.

Banyak protokol lain (seperti SONET) menggunakan bentuk yang berbeda encoding dikenal sebagai scrambling jam untuk menanamkan informasi ke dalam data stream. Spesifikasi PCIe juga mendefinisikan algoritma scrambling, tetapi digunakan untuk mengurangi interferensi elektromagnetik (EMI) dengan mencegah pola berulang data dalam aliran data yang ditransmisikan.

Data link layer

Data Link Layer melakukan tiga layanan penting untuk PCIe tautan mengungkapkan:

urutan transaksi lapisan paket (TLP) yang dihasilkan oleh lapisan transaksi,

memastikan pengiriman yang dapat diandalkan TLP antara dua endpoint melalui protokol pengakuan (ACK dan NAK sinyal) yang secara eksplisit mengharuskan replay diakui / buruk TLP,

menginisialisasi dan mengelola kredit kontrol aliran

Di sisi mengirimkan, lapisan data link menghasilkan urutan nomor incrementing untuk setiap TLP keluar. Ini berfungsi sebagai tag identifikasi unik untuk setiap TLP ditransmisikan, dan dimasukkan ke dalam header dari keluar TLP. A 32-bit kode cyclic redundancy check (dikenal dalam konteks ini sebagai link CRC atau LCRC) juga ditambahkan ke akhir setiap TLP keluar.

Di sisi receive, LCRC menerima TLP dan nomor urut keduanya divalidasi pada lapisan link. Jika salah satu cek LCRC gagal (menunjukkan kesalahan data), atau urutan-nomor di luar jangkauan (non-berturut-turut dari terakhir yang valid diterima TLP), maka buruk TLP, serta setiap TLP diterima setelah TLP buruk, dianggap tidak valid dan dibuang. Penerima mengirimkan pesan pengakuan negatif (NAK) dengan urutan-jumlah TLP valid, meminta kembali transmisi semua TLP maju itu urutan-nomor. Jika menerima TLP melewati pemeriksaan LCRC dan memiliki nomor urutan yang benar, itu dianggap sah. Kenaikan Link Penerima urutan-nomor (yang melacak terakhir diterima TLP baik), dan meneruskan TLP sah untuk transaksi lapisan penerima. Pesan ACK dikirim ke pemancar jarak jauh, yang menunjukkan TLP berhasil diterima (dan dengan perpanjangan, semua TLP dengan masa lalu-urutan nomor.)

Jika pemancar menerima pesan NAK, atau tidak ada pengakuan (NAK atau ACK) diterima sampai batas waktu berakhir, pemancar harus retransmit semua TLP yang tidak memiliki pengakuan positif (ACK). Cegah kerusakan terus-menerus dari perangkat atau media transmisi, link-layer menyajikan koneksi yang handal ke lapisan transaksi, karena protokol transmisi memastikan pengiriman TLP melalui media tidak dapat diandalkan.

Selain mengirim dan menerima TLP dihasilkan oleh lapisan transaksi, lapisan data-link juga menghasilkan dan mengkonsumsi DLLPs, data link lapisan paket. Nak ACK dan sinyal yang dikomunikasikan melalui DLLPs, seperti informasi kontrol aliran kredit, beberapa pesan manajemen daya dan arus informasi kredit kontrol (atas nama lapisan transaksi.)

Dalam prakteknya, jumlah in-flight, TLP diakui pada link dibatasi oleh dua faktor: ukuran buffer replay transmitter (yang harus menyimpan salinan semua TLP dikirimkan sampai penerima remote ACK mereka), dan kontrol aliran kredit yang dikeluarkan oleh penerima dengan pemancar. PCI Express mengharuskan semua penerima untuk mengeluarkan jumlah minimum kredit, untuk menjamin link memungkinkan pengiriman TLP PCIConfig dan TLP pesan.

Lapisan Transaksi

PCI Express menerapkan transaksi dibagi (transaksi dengan permintaan dan respon yang dipisahkan oleh waktu), memungkinkan link untuk membawa lalu lintas lainnya sementara target perangkat mengumpulkan data untuk tanggapan.

PCI Express menggunakan kontrol aliran berbasis kredit. Dalam skema ini, perangkat Advertises awal jumlah kredit untuk setiap buffer diterima dalam lapisan transaksinya. Perangkat di ujung link, bila mengirim transaksi ke perangkat ini, menghitung jumlah kredit masing-masing TLP mengkonsumsi dari rekeningnya. Perangkat pengirim hanya dapat mengirimkan TLP ketika hal tersebut tidak membuat hitungan kredit konsumsi yang melebihi batas kredit. Bila perangkat penerima selesai memproses TLP dari buffer, maka sinyal kembali kredit ke perangkat pengirim, yang meningkatkan batas kredit dengan jumlah yang dikembalikan. Counter kredit counter modular, dan perbandingan kredit untuk dikonsumsi batas kredit memerlukan aritmatika modular. Keuntungan dari skema ini (dibandingkan dengan metode lain seperti negara atau menunggu berbasis protokol transfer jabat tangan) adalah bahwa latency kredit kembali tidak mempengaruhi kinerja, asalkan batas kredit tidak ditemui. Asumsi ini biasanya bertemu jika setiap perangkat dirancang dengan ukuran yang cukup penyangga.

PCIe 1.x sering dikutip untuk mendukung data rate 250 MB / s di setiap arah, per jalur. Angka ini merupakan perhitungan dari fisik signaling menilai (2,5 Gbaud) dibagi dengan encoding overhead (10 bits per byte.) Ini berarti enambelas lane (× 16) PCIe kartu kemudian akan secara teoritis akan mampu 16 × 250 MB / s = 4 GB / s di setiap arah. Sementara ini benar dalam hal data byte, lebih bermakna perhitungan didasarkan pada data payload menilai, yang tergantung pada profil lalu lintas, yang merupakan fungsi dari tingkat tinggi aplikasi (software) dan protokol tingkat intermediate.

Seperti data rate serial sistem interkoneksi tinggi lainnya, PCIe memiliki protokol dan pengolahan overhead karena tambahan transfer kesegaran (CRC dan pengakuan). Panjang terus unidirectional transfer (seperti yang khas dalam pengontrol penyimpanan berkinerja tinggi) bisa mendekati> 95% dari baku (jalur) data rate PCIe. Ini transfer juga memperoleh keuntungan dari peningkatan jumlah Lanes (× 2, × 4, dll) Namun dalam aplikasi yang lebih khas (seperti USB atau Ethernet controller), lalu lintas adalah profil karakteristik sebagai data paket singkat dengan sering enforced Penghargaan

Jenis lalu lintas mengurangi efisiensi link, karena overhead dari paket parsing interrupts dan dipaksa (baik dalam perangkat antarmuka host atau PC CPU.) Menjadi protokol untuk perangkat yang terhubung ke papan sirkuit cetak yang sama, tidak memerlukan toleransi yang sama untuk transmisi kesalahan sebagai protokol untuk komunikasi jarak yang lebih jauh, dan dengan demikian, ini kehilangan efisiensi tidak khusus untuk PCIe.

Eksternal kartu PCIe

Secara teoritis, eksternal PCIe notebook dapat memberikan kekuatan grafis dari desktop, dengan menghubungkan notebook dengan kartu desktop video PCIe (terlampir dalam perumahan eksternal sendiri, dengan power supply yang kuat dan pendinginan), mungkin dengan sebuah antarmuka ExpressCard atau antarmuka Thunderbolt . Antarmuka ExpressCard menyediakan bit rate dari 5 Gbit / s (0,5 GB / s throughput yang), sedangkan antarmuka Thunderbolt menyediakan bit rate hingga 10 Gb / s (1 GB / s throughput yang). Namun, kartu video high-end bisa naik ke PCIe 3.0 × 16, yang dapat mentransfer pada 128 Gbit / s (15,75 GB / s), yang berarti transfer data ke kartu video eksternal dapat melakukan 10 kali lebih lambat daripada kartu video terhubung langsung ke motherboardIBM / Lenovo juga termasuk slot PCI-Express di Docking Station 250310U lanjutan mereka. Ini menyediakan slot berukuran setengah dengan × 16 soket panjang, tetapi hanya × 1 konektivitas.

Namun, stasiun docking dengan slot ekspansi menjadi kurang umum sebagai laptop mendapatkan kartu lebih maju video dan baik antarmuka DVI-D, atau DVI-D untuk melewati replikator pelabuhan dan stasiun docking.

Selain itu, Nvidia Quadro Plex telah mengembangkan eksternal PCIe video card yang dapat digunakan untuk aplikasi grafis canggih. Ini memerlukan kartu video PCI Express × 8 atau × 16 slot untuk kabel interkoneksi. [48] Pada tahun 2008, AMD mengumumkan ATI XGP teknologi, didasarkan pada sistem kabel milik yang kompatibel dengan PCIe × 8 transmisi sinyal.

Konektor ini tersedia di Fujitsu Amilo dan Acer Ferrari One notebook. Hanya Fujitsu memiliki kotak eksternal yang sebenarnya tersedia, yang juga bekerja pada Ferrari One. Baru-baru ini Acer meluncurkan dermaga grafis Dynavivid untuk XGP.

Sekarang ada kartu hubs dalam pembangunan yang satu dapat terhubung ke laptop melalui slot ExpressCard, meskipun mereka saat ini sedang langka, mengaburkan, atau tidak tersedia di pasar terbuka. Hub ini dapat menerima kartu berukuran penuh.

Magma dan ViDock juga menggunakan ExpressCard dan menerapkan penggunaan sistem grafis eksternal. ViDock besarbesaran casis ekspansi dirancang khusus untuk beradaptasi PCI Express kartu grafis untuk digunakan dengan ExpressCard dilengkapi komputer portabel. Hal ini memungkinkan menghubungkan kartu PCIe eksternal. Perkembangan teknologi ini masih berkembang, contoh lainnya adalah MSI GUS, Stasiun XG Asus.

Baru-baru ini, Intel dan Apple memperkenalkan Thunderbolt, memungkinkan untuk PCI (e) perangkat eksternal untuk mentransfer dua kali lipat kecepatan antarmuka ExpressCard. Namun kartu video eksternal mid-range masih akan sangat mencekik oleh koneksi yang lambat.

Thunderbolt telah memberikan kesempatan kepada produk-produk baru dan lebih cepat untuk berhubungan dengan kartu PCIe eksternal. Magma telah merilis 3T ExpressBox, yang dapat menampung hingga tiga kartu PCIe (dua pada 8 × dan satu di 4 ×), hal ini memungkinkan untuk workstation lebih baik ketika notebook tidak memiliki banyak port. MSI juga merilis Thunderbolt GUS II, chassis PCIe didedikasikan untuk produk cards.Other video seperti Soneta Echo Express dan mLink mLogic adalah Thunderbolt PCIe chassis dalam bentuk yang lebih kecil, ini memungkinkan konektivitas ke low-profile kartu video, kartu suara, kartu jaringan, memori, penyimpanan, dll

Namun, semua produk ini memerlukan penggunaan port Thunderbolt (yaitu perangkat Thunderbolt), membuat mereka kompatibel dengan sebagian besar komputer.

Memori eksternal

PCI protokol Express dapat digunakan sebagai interface data ke perangkat memori flash, seperti kartu memori dan solid state drive. Satu format tersebut adalah kartu XQD dikembangkan oleh Asosiasi CompactFlash, SATA Expressand SCSI Express.

Banyak kinerja tinggi, kelas enterprise solid state drive dirancang sebagai PCI Express RAID controller dengan kartu chip memori flash ditempatkan langsung pada papan sirkuit, hal ini memungkinkan kecepatan transfer yang lebih tinggi (lebih dari 1 GByte / s) dan operasi I / O IOPS ( per detik) (lebih dari 1 juta) dibandingkan dengan Serial ATA atau drive SAS.

OCZ dan Marvell co-mengembangkan native PCIe solid state drive controller Kilimanjaro yang digunakan dalam OCZ Z-Drive 5. Z-Drive 5 ini dirancang untuk PCIe 3.0 × 16 slot bila kapasitas tertinggi (12 TB) versi dipasang di dalam slot tersebut dapat berjalan hingga 7,2 gigabyte per detik dan sekuensial transfer hingga 2,52 juta IOPS di transfer acak .

Protokol Bersaing

Beberapa standar komunikasi telah muncul berdasarkan bandwidth tinggi serial arsitektur. Ini termasuk InfiniBand, RapidIO, HyperTransport, QPI dan StarFabric. Perbedaan didasarkan pada timbal balik antara fleksibilitas dan diperpanjang vs latency dan overhead. Sebuah contoh seperti ini adalah tradeoff kompleks menambahkan informasi header ke paket yang dikirim untuk kompleks routing (PCI Express tidak mampu ini). Penambahan biaya overhead mengurangi bandwidth efektif antarmuka dan mempersulit penemuan bus dan perangkat lunak inisialisasi. Juga membuat sistem hot-pluggable mengharuskan software melacak perubahan topologi jaringan. Contoh bis cocok untuk tujuan ini adalah InfiniBand dan StarFabric.

Contoh lain adalah membuat paket yang singkat untuk menurunkan latency (sebagaimana diperlukan jika bus harus beroperasi sebagai antarmuka memori). Paket yang lebih kecil berarti paket header mengkonsumsi persentase yang lebih tinggi dari paket, sehingga mengurangi bandwidth efektif. Contoh protokol bus yang dirancang untuk tujuan ini adalah RapidIO dan HyperTransport.

PCI Express jatuh di suatu tempat di tengah, sasaran desain sebagai sistem interkoneksi (bus lokal) daripada perangkat interkoneksi atau protokol jaringan routed. Selain itu, tujuan desain software transparansi constrains protokol dan meningkatkan latency-nya sedikit.

Pengembangan alat

Ketika mengembangkan dan / atau tips PCI Express bus, pemeriksaan sinyal perangkat keras dapat menjadi sangat penting untuk menemukan masalah. Osiloskop, analisa logika dan analisa bus adalah alat yang mengumpulkan, menganalisis, decode, menyimpan sinyal sehingga orang dapat melihat bentuk gelombang kecepatan tinggi di waktu luang mereka.

Nah itulah Pengertian tentang PCIe Yang belu tahu silahankan di baca jangan Lupa like Fanspagena dan Follow ya twitternya,,,,,,,,,,,

PCIe (Peripheral Component Interconnect Express), resmi disingkat sebagai PCIe, adalah standar serial kecepatan tinggi komputer expansion bus yang dirancang untuk menggantikan PCI tua, PCI-X, dan standar AGP bus. PCIe memiliki banyak perbaikan atas standar bus tersebut, termasuk Throughput sistem bus maksimum yang lebih tinggi, lebih rendah I / O jumlah pin dan jejak fisik lebih kecil, lebih baik kinerja-scaling untuk perangkat bus, deteksi kesalahan yang lebih rinci mekanisme dan pelaporan (Advanced Error Reporting (AER ),Dan fungsi hot-plug asli. Revisi lebih baru dari PCIe standar dukungan hardware I / O virtualisasi.

Antarmuka listrik PCIe juga digunakan dalam berbagai standar lainnya, terutama ExpressCard, antarmuka kartu ekspansi laptop.

Spesifikasi Format dipelihara dan dikembangkan oleh PCI-SIG (PCI Special Interest Group), sebuah kelompok lebih dari 900 perusahaan yang juga mempertahankan spesifikasi PCI konvensional. PCIe 3.0 adalah standar terbaru untuk kartu ekspansi yang ada di produksi dan tersedia pada komputer pribadi utama

Aplikasi

PCI Express beroperasi di konsumen, server dan aplikasi industri, sebagai Motherboard level interkoneksi (untuk menghubungkan Motherboard-mount peripheral), backplane interkoneksi pasif dan sebagai antarmuka kartu ekspansi untuk add-in papan.

Dalam hampir semua modern (pada 2012) PC, laptop dari konsumen dan desktop ke server data perusahaan, bus PCIe berfungsi sebagai interkoneksi motherboard-tingkat dasar, menghubungkan sistem host-prosesor dengan kedua terpadu peripheral (permukaan-mount IC) dan add-on peripheral (kartu ekspansi.) Dalam sebagian besar sistem ini, bus PCIe co-ada dengan satu atau lebih warisan PCI bus, untuk kompatibilitas dengan tubuh besar warisan PCI peripheral.

Arsitektur

onceptually, bus PCIe seperti pengganti serial kecepatan tinggi yang lebih tua PCI / PCI-X bus,

bus interkoneksi menggunakan shared alamat / data baris.

Perbedaan utama antara PCIe bus dan PCI tua adalah topologi bus. PCI menggunakan arsitektur bus paralel bersama, di mana tuan rumah PCI dan semua perangkat berbagi seperangkat alamat / data / kontrol garis. Sebaliknya, PCIe didasarkan pada topologi point-to-point, dengan link serial yang terpisah menghubungkan setiap perangkat ke kompleks akar (host). Karena topologi bus nya bersama, akses ke PCI bus lebih tua arbitrated (dalam kasus beberapa master), dan terbatas pada satu master pada suatu waktu, dalam satu arah. Selain itu, yang lebih tua PCI clocking skema membatasi jam bus ke paling lambat perifer di bus (terlepas dari perangkat yang terlibat dalam transaksi bus). Sebaliknya, link bus PCIe mendukung komunikasi full-duplex antara dua endpoint, dengan tidak ada pembatasan yang melekat pada akses bersamaan di beberapa endpoints.

Dalam hal protokol bus, PCIe komunikasi dirumuskan dalam paket. Pekerjaan data packetizing dan de-packetizing dan status pesan lalu lintas ditangani oleh lapisan transaksi port PCIe (dijelaskan kemudian). Radikal perbedaan sinyal listrik dan protokol bus memerlukan penggunaan faktor bentuk yang berbeda mekanik dan konektor ekspansi (dan dengan demikian, motherboard baru dan papan adaptor baru), slot PCI dan slot PCIe tidak saling dipertukarkan. Pada tingkat perangkat lunak, PCIe menjaga kompatibilitas dengan PCI; warisan perangkat lunak sistem PCI dapat mendeteksi dan mengkonfigurasi perangkat PCIe baru tanpa dukungan eksplisit untuk standar PCIe, meskipun fitur baru PCIe tidak dapat diakses.

PCIe link antara dua perangkat dapat terdiri dari mana saja 1-32 jalur. Dalam multi-link lane, paket data bergaris-garis di jalur, dan puncak skala data throughput yang dengan lebar keseluruhan link. Hitungan jalur secara otomatis dinegosiasikan selama inisialisasi perangkat, dan dapat dibatasi oleh salah satu endpoint. Misalnya, PCIe (× 1) kartu-jalur tunggal dapat dimasukkan ke dalam slot multi-lane (× 4, 8 ×, dll), dan siklus inisialisasi auto-menegosiasikan jumlah jalur saling mendukung tertinggi. Link dapat dinamis down-link mengkonfigurasi untuk menggunakan jalur yang lebih sedikit, sehingga memberikan beberapa ukuran toleransi kegagalan di hadapan jalur buruk atau tidak dapat diandalkan. Standar PCIe mendefinisikan slot dan konektor untuk beberapa lebar: × 1, × 4, 8 ×, × 16 × 32. Hal ini memungkinkan PCIe bus untuk melayani kedua aplikasi biaya-sensitif di mana throughput yang tinggi tidak diperlukan, serta aplikasi kinerja-kritis seperti grafis 3D, jaringan (10 Gigabit Ethernet, Gigabit Ethernet multiport), dan perusahaan penyimpanan (SAS, Fibre Channel. )

Sebagai titik acuan, perangkat PCI-X (133 MHz 64-bit) dan PCIe perangkat pada 4-jalur (× 4), Gen1 kecepatan memiliki kira-kira kecepatan transfer puncak yang sama dalam satu-arah: 1.064 MB / sec. Bus PCIe memiliki potensi untuk melakukan lebih baik daripada bus PCI-X dalam kasus di mana beberapa perangkat yang mentransfer data berkomunikasi secara bersamaan, atau jika komunikasi dengan PCIe perifer adalah dua arah.

Penghubung

Perangkat PCIe berkomunikasi melalui koneksi logis disebut link interconnector. Sebuah link adalah saluran komunikasi point-to-point antara dua port PCIe, yang memungkinkan baik untuk mengirim / menerima biasa PCI-permintaan (konfigurasi membaca / menulis, I / O membaca / menulis, memori baca / tulis) dan interupsi (INTx, MSI , MSI-X). Pada tingkat fisik, link terdiri dari 1 atau lebih jalur. kecepatan rendah periferal (seperti 802.11 Wi-Fi card) menggunakan jalur tunggal (× 1) link, sedangkan adapter grafis biasanya menggunakan lebih luas (dan dengan demikian, lebih cepat) Link 16-lane.

Jalur

Jalur A terdiri dari dua pasang diferensial sinyal: satu pasang untuk menerima data, yang lain untuk transmisi. Dengan demikian, masing-masing jalur terdiri dari empat kabel atau sinyal jejak. Secara konseptual, masing-masing jalur digunakan sebagai aliran byte full-duplex, mengangkut paket data dalam format delapan-bit 'byte', antara endpoint dari link, di kedua arah secara bersamaan [6] Fisik slot PCIe mungkin berisi 1-30-. dua jalur, dalam kekuatan dari dua (1, 2, 4, 8, 16 dan 32) jumlah Lane ditulis dengan awalan × (misalnya, × 16 merupakan kartu enam belas jalur atau Slot), dengan × 16 menjadi ukuran terbesar umum dipakai

Serial bus

The berikat serial format dipilih lebih tradisional Format bus paralel karena keterbatasan yang terakhir, termasuk operasi tunggal-duplex, jumlah sinyal kelebihan dan bandwidth inheren lebih rendah karena waktu miring. Timing miring hasil dari sinyal-sinyal listrik yang terpisah dalam antarmuka paralel bepergian ke konduktor yang berbeda-panjang, pada potensi yang berbeda sirkuit lapisan papan tercetak, dengan kecepatan sinyal yang mungkin berbeda. Meskipun ditransmisikan secara bersamaan sebagai satu kata, sinyal pada antarmuka paralel pengalaman waktu perjalanan yang berbeda dan tiba di tujuan mereka pada saat-saat yang berbeda. Ketika clock rate antarmuka meningkat ke titik di mana kebalikannya (yaitu, periode clock) lebih pendek dari yang mungkin waktu terbesar antara kedatangan sinyal, sinyal tidak lagi datang dengan kebetulan cukup untuk membuat pemulihan dari kata ditransmisikan mungkin. Karena waktu miring atas bus paralel dapat berjumlah beberapa nanodetik, keterbatasan bandwidth yang dihasilkan dalam kisaran ratusan megahertz.

Sebuah antarmuka serial tidak menunjukkan waktu miring karena hanya ada satu sinyal diferensial di setiap arah dalam setiap jalur, dan tidak ada sinyal clock eksternal karena informasi clocking tertanam dalam sinyal serial. Dengan demikian, keterbatasan bandwidth yang khas pada sinyal serial dalam kisaran multi-gigahertz. PCIe hanyalah satu contoh dari kecenderungan umum dari bus paralel ke serial interkoneksi. Contoh lain termasuk Serial ATA, USB, SAS, FireWire (1394) dan RapidIO.

Desain serial Multichannel meningkatkan fleksibilitas dengan mengalokasikan perangkat lambat untuk jalur kurang dari perangkat cepat.

Faktor bentuk

PCI Express (standard)

Sebuah kartu PCIe cocok menjadi slot ukuran fisik atau lebih besar (maksimum × 16), tetapi tidak masuk ke dalam slot PCIe lebih kecil (misalnya, × 16 kartu dalam × 8 Slot). Beberapa slot menggunakan soket terbuka untuk mengizinkan kartu fisik lagi dan menegosiasikan sambungan listrik terbaik yang tersedia. Jumlah jalur sebenarnya terhubung ke slot mungkin juga kurang dari jumlah didukung oleh ukuran slot fisik.

Contohnya adalah × 8 Slot yang sebenarnya hanya berjalan pada × 1. Slot ini memungkinkan setiap × 1, × 2, × 4 atau 8 × kartu, meskipun hanya berjalan pada kecepatan × 1. Jenis socket disebut × 8 (× 1 mode) Slot, berarti secara fisik menerima hingga × 8 kartu tetapi hanya berjalan pada kecepatan × 1. Hal ini juga kadang-kadang ditetapkan sebagai "× Ukuran (@ × kapasitas)" (misalnya, "× 16 (@ × 8)"). Keuntungannya adalah bahwa hal itu dapat menampung kisaran yang lebih besar dari kartu PCIe tanpa membutuhkan hardware motherboard untuk mendukung kecepatan transfer penuh. Hal ini membuat desain dan biaya implementasi bawah.

|

Various PCI slots. From top to bottom:

|

Di tabel berikut mengidentifikasi konduktor pada setiap sisi konektor tepi pada kartu PCI Express. Sisi solder dari printed circuit board (PCB) adalah sisi A, dan sisi komponen adalah B side.PRSNT1 # dan PRSNT2 # pin harus sedikit lebih pendek daripada yang lain, untuk memastikan bahwa kartu hot-terpasang sepenuhnya dimasukkan . The WAKE # pin menggunakan tegangan penuh untuk membangunkan komputer, tetapi harus ditarik tinggi dari daya siaga untuk menunjukkan bahwa kartu tersebut mampu bangun.

Semua ukuran × 4 dan 8 × kartu PCI Express diperbolehkan konsumsi daya maksimum 25 W. Semua × 1 kartu yang awalnya 10 W, kartu tinggi penuh dapat mengkonfigurasi dirinya sendiri sebagai 'daya tinggi' mencapai 25 W, sementara setengah -height × 1 kartu adalah tetap pada 10 W. Semua ukuran × 16 kartu yang awalnya 25 W, seperti × 1 kartu, kartu setengah tinggi terbatas ke nomor ini sementara kartu tinggi penuh dapat meningkatkan kekuatan mereka setelah konfigurasi. Mereka dapat menggunakan hingga 75 W (3,3 V / 3 A + 12 V/5.5 A), meskipun spesifikasi menuntut bahwa konfigurasi yang lebih tinggi-daya digunakan untuk kartu grafis saja, sedangkan kartu tujuan lainnya adalah untuk tetap pada 25 konektor WOptional tambahkan 75 W (6-pin) dan / atau 150 W (8-pin) daya hingga 525 W total (75 W + 3 × 150 W).

Kartu Mini PCI Express (Mini card PCIe)

|

| A WLAN PCI Express Mini Card and its connector. |

Dimensi fisik

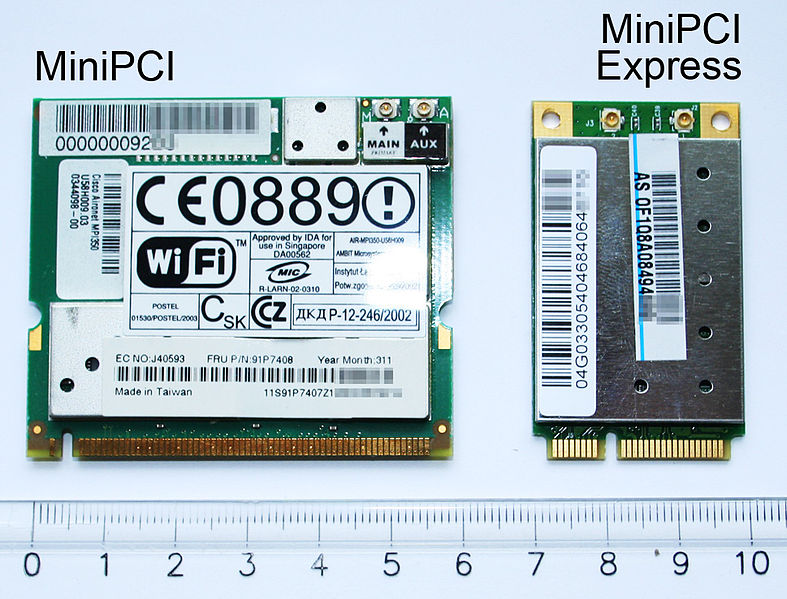

|

| MiniPCI and MiniPCI Express cards in comparison |

listrik Interface

Mini PCI Express konektor tepi Card menyediakan beberapa koneksi dan bus:

PCIe × 1

USB 2.0

SMBus

Kabel untuk diagnostik LED untuk jaringan nirkabel (yaitu, Wi-Fi) status pada chassis komputer

Kartu SIM untuk aplikasi GSM dan WCDMA. (Sinyal UIM di spec)

Perpanjangan masa depan untuk lain PCIe lane

1,5 dan 3,3 volt

Mini PCI Express & mSATA

Meskipun berbagi mini-PCI Express faktor bentuk, slot mSATA belum tentu elektrik kompatibel dengan Mini PCI Express. Untuk alasan ini, hanya notebook tertentu yang kompatibel dengan mSATA drive. Kebanyakan sistem kompatibel didasarkan pada arsitektur prosesor Intel Sandy Bridge, menggunakan platform Huron River. Tapi untuk konektor mSATA / mini-PCI-E, satu-satunya prasyarat adalah bahwa ada sebuah saklar yang membuatnya baik mSATA atau slot mini PCI-E dan dapat diimplementasikan pada platform apapun.

Notebook Lenovo seperti T-Series, W-Series, dan X-Series ThinkPad dirilis pada bulan Maret-April 2011 memiliki dukungan untuk kartu SSD mSATA dalam slot kartu WWAN mereka. The ThinkPad Edge E220s/E420s, dan Lenovo IdeaPad Y460/Y560 juga mendukung mSATA

Beberapa notebook (terutama Asus Eee PC, Apple MacBook Air, dan Dell mini9 dan mini10) menggunakan varian dari Kartu Mini PCI Express sebagai SSD. Varian ini menggunakan pin non-reserved pendiam dan beberapa untuk melaksanakan SATA dan IDE antarmuka passthrough, hanya menjaga USB, garis tanah, dan kadang-kadang inti PCIe 1x bus utuh. [14] Hal ini membuat flash 'miniPCIe' dan solid state drive dijual untuk netbook sebagian besar tidak sesuai dengan benar Mini PCI Express implementasi.

Juga, khas Asus miniPCIe SSD adalah 71 mm panjang, menyebabkan mm Model Dell 51 sampai sering menjadi (salah) disebut sebagai setengah panjang. Benar 51 mm Mini PCIe SSD diumumkan pada tahun 2009, dengan dua ditumpuk PCB lapisan, yang memungkinkan untuk kapasitas penyimpanan yang lebih tinggi. Mengumumkan desain mempertahankan antarmuka PCIe, sehingga kompatibel dengan standar Mini slot PCIe. Tidak ada produk kerja yang belum dikembangkan.

Intel Desktop Board memiliki banyak dengan PCIe × 1 slot Mini-Card yang biasanya tidak mendukung mSATA SSD. Daftar Dewan Desktop yang native mendukung mSATA di PCIe x1 slot Mini-Card (biasanya multiplexing dengan port SATA) disediakan pada situs Dukungan Intel

PCI Express Eksternal Kabel

PCI Express Eksternal Kabel (juga dikenal sebagai Eksternal PCI Express, kabel PCI Express, atau ePCIe) spesifikasi yang dirilis oleh PCI-SIG pada Februari 2007. Kabel dan konektor standar telah ditetapkan untuk × 1, × 4, 8 ×, dan 16 × lebar link, dengan transfer rate 250 MB / s per jalur. PCI-SIG juga mengharapkan norma akan berkembang mencapai 500 MB / s, seperti dalam PCI Express 2.0. Panjang kabel maksimum tetap belum ditentukan. Sebuah contoh dari penggunaan kabel PCI Express adalah kandang logam, yang mengandung sejumlah slot PCI dan sirkuit adapter PCI-to-ePCIe. Perangkat ini tidak akan mungkin kalau bukan untuk spec ePCIe.

Bentuk derivatif

Ada beberapa jenis kartu ekspansi lain yang berasal dari PCIe. Ini termasuk:

Low height card

ExpressCard: penerus faktor bentuk PC Card (dengan × 1 PCIe dan USB 2.0, hot-pluggable)

PCI Express ExpressModule: faktor bentuk modular hot-pluggable yang ditetapkan untuk server dan workstation

Kartu XQD: a berbasis PCI Express kartu flash standar oleh Asosiasi CompactFlash

XMC: mirip dengan CMC / PMC form factor (VITA 42.3)

AdvancedTCA: pelengkap CompactPCI untuk aplikasi yang lebih besar, mendukung topologi backplane berbasis seri

AMC: pelengkap spesifikasi AdvancedTCA, mendukung prosesor dan I / O modul pada ATCA papan (× 1, × 2, × 4 atau 8 × PCIe).

FeaturePak: format kecil kartu ekspansi (43 × 65 mm) untuk embedded dan aplikasi faktor bentuk kecil, melainkan mengimplementasikan dua × 1 PCIe link pada konektor kepadatan tinggi bersama dengan USB, I2C, dan hingga 100 poin dari I / O.

Universal IO: Sebuah varian dari Super Micro Computer Inc dirancang untuk digunakan dalam rak low profile mount chassis. Ini telah braket konektor terbalik sehingga tidak dapat disimpan dalam sebuah PCI Express soket normal, tapi pin yang kompatibel dan dapat dimasukkan jika braket akan dihapus.

Thunderbolt: Sebuah varian dari Intel dan Apple yang menggabungkan DisplayPort dan protokol PCIe dalam faktor bentuk yang kompatibel dengan Mini DisplayPort.

Serial Digital Video Out: beberapa 9xx series chipset Intel memungkinkan untuk menambahkan output tambahan untuk video terintegrasi ke slot PCIe (kebanyakan berdedikasi dan 16 jalur)

Sejarah dan revisi

PCIe adalah teknologi dalam pembangunan konstan dan perbaikan. PCI ekspres implementasi saat ini adalah versi 3.0.

PCI Express 1.0a

|

| Kartu yang MenggunakanPCIe 1.0a |

Pada tahun 2003, PCI-SIG memperkenalkan PCIe 1.0a, dengan per-jalur data rate 250 MB / s dan kecepatan transfer 2,5 gigatransfers per detik (GT / s). Transfer rate dinyatakan dalam transfer per detik bukan bit per detik karena jumlah transfer termasuk bit overhead, yang tidak memberikan throughput tambahan.

PCIe 1.x menggunakan skema encoding 8B/10B yang menghasilkan 20 persen ((10-8) / 10) overhead pada tingkat bit mentah. Ini menggunakan clock rate 2,5 GHz, sehingga memberikan efektif 250 000 000 byte per detik (250 MB / s) data rate maksimum.

PCI Express 1.1

Pada tahun 2005, PCI-SIG diperkenalkan PCIe 1.1. Spesifikasi ini diperbarui termasuk klarifikasi dan beberapa perbaikan, tetapi sepenuhnya kompatibel dengan PCI Express 1.0a. Tidak ada perubahan yang dilakukan pada data rate.

PCI Express 2.0

PCI-SIG mengumumkan ketersediaan PCI Express 2.0 Basis spesifikasi pada 15 Januari 2007

2,0 standar PCIe menggandakan kecepatan transfer dibandingkan dengan PCIe 1,0-5 GT / s dan throughput per-jalur naik dari 250 MB / s hingga 500 MB / s. Ini berarti 32-lane konektor PCIe (× 32) dapat mendukung throughput hingga 16 GB / s agregat.

PCIe 2.0 slot motherboard sepenuhnya kompatibel dengan PCIe kartu v1.x. PCIe 2.0 kartu juga umumnya kompatibel dengan motherboard PCIe 1.x, menggunakan bandwidth PCI Express 1.1. Secara keseluruhan, kartu grafis atau motherboard dirancang untuk v2.0 akan bekerja dengan v1.1 yang lain atau 1.0a.

PCI-SIG juga mengatakan bahwa PCIe 2.0 memiliki fitur perbaikan data point-to-point protokol transfer dan arsitektur perangkat lunak.

Pertama PCIe 2.0 chipset mampu Intel adalah X38 dan papan mulai kapal dari berbagai vendor (Abit, Asus, Gigabyte) pada tanggal 21 Oktober, 2007AMD mulai mendukung PCIe 2.0 dengan AMD 700 series chipset dan nVidia dimulai dengan MCP72All chipset sebelum Intel , termasuk chipset Intel P35, didukung PCIe 1.1 atau 1.x 1.0aLike, PCIe 2.0 menggunakan skema encoding 8B/10B, sehingga memberikan, per jalur, sebuah 4 Gbit / s max transfer rate efektif dari yang 5 GT / s baku data rate.

PCI Express 2.1

PCI Express 2.1 mendukung sebagian besar dari manajemen, dukungan, dan sistem pemecahan masalah direncanakan untuk implementasi penuh pada PCI Express 3.0. Namun, kecepatan adalah sama dengan PCI Express 2.0.

PCI Express 3.0

PCI Express 3.0 Basis spesifikasi revisi 3.0 dibuat tersedia pada November 2010, setelah beberapa penundaan. Pada bulan Agustus 2007, PCI-SIG mengumumkan bahwa PCI Express 3.0 akan membawa bit rate dari 8 gigatransfers per detik (GT / s), dan bahwa hal itu akan kompatibel dengan implementasi PCIe yang ada. Pada saat itu, ia juga mengumumkan bahwa spesifikasi final untuk PCI Express 3.0 akan ditunda sampai 2011

Fitur baru untuk spesifikasi PCIe 3.0 termasuk sejumlah optimasi untuk meningkatkan sinyal dan integritas data, termasuk pemancar dan penerima pemerataan, peningkatan PLL, jam pemulihan data, dan perangkat tambahan saluran untuk saat ini didukung topologi.

Setelah analisis teknis enam bulan kelayakan skala bandwidth interkoneksi PCIe, analisis PCI-SIG menemukan bahwa 8 gigatransfers per detik dapat diproduksi dalam arus utama teknologi proses silikon, dan dapat digunakan dengan bahan murah yang ada dan infrastruktur, sambil mempertahankan kompatibilitas penuh (dengan dampak yang dapat diabaikan) ke PCIe stack protokol.

PCIe 3.0 upgrade skema pengkodean untuk 128b/130b dari 8b/10b sebelumnya, mengurangi biaya overhead menjadi sekitar 1,54% ((130-128) / 130), yang bertentangan dengan 20% dari PCIe 2.0. Hal ini dicapai dengan teknik yang disebut "scrambling" yang berlaku biner polinomial yang dikenal dengan aliran data dalam topologi umpan balik. Karena jumlahnya banyak berebut diketahui, data dapat dipulihkan dengan menjalankan melalui topologi umpan balik menggunakan polinomial terbalik

PCIe 3.0 's 8 tingkat GT / s bit efektif memberikan 985 MB / s per jalur, ganda PCIe 2.0 bandwidth. PCI-SIG mengharapkan PCIe 3.0 spesifikasi untuk menjalani pemeriksaan teknis yang ketat dan validasi sebelum dirilis ke industri. Proses ini, yang diikuti dalam pengembangan generasi sebelumnya Basis PCIe dan faktor bentuk berbagai spesifikasi, termasuk bukti yang menguatkan parameter listrik akhir dengan data yang berasal dari silikon tes dan simulasi lainnya yang dilakukan oleh beberapa anggota PCI-SIG.

Pada tanggal 18 November 2010, PCI Special Interest Group secara resmi menerbitkan diselesaikan PCI Express 3.0 spesifikasi kepada para anggotanya untuk membangun perangkat berdasarkan versi baru PCI Express.

Kartu AMD andalan terbaru grafis, Radeon HD 7970, diluncurkan pada tanggal 9 Januari 2012, pertama PCIe 3.0 kartu grafis dunia. ulasan awal menunjukkan bahwa antarmuka baru tidak akan meningkatkan kinerja grafis dibandingkan dengan sebelumnya PCIe 2.0, yang pada saat penulisan, masih kurang dimanfaatkan. Namun, antarmuka baru akan terbukti menguntungkan bila digunakan untuk tujuan umum komputasi dengan teknologi seperti OpenCL, CUDA, dan C + + AMP.

PCI Express 4.0

Pada tanggal 29 November 2011, PCI-SIG mengumumkan PCI Express 4.0 menampilkan 16 GT / s, masih didasarkan pada teknologi tembaga. Selain itu, aktif dan siaga optimasi Daya untuk diselidiki. Spesifikasi final diharapkan akan dirilis pada 2014-15

Status saat ini

Pada 2013 PCI Express telah menggantikan AGP sebagai antarmuka default untuk kartu grafis pada sistem baru. Hampir semua model kartu grafis dirilis sejak 2010 oleh AMD (ATI) dan NVIDIA menggunakan PCI Express. NVIDIA menggunakan transfer data bandwidth tinggi dari PCIe untuk perusahaan Scalable Link Interface (SLI) teknologi, yang memungkinkan beberapa kartu grafis dari chipset yang sama dan nomor model untuk berjalan secara bersamaan, yang memungkinkan peningkatan kinerja. AMD juga telah mengembangkan sistem multi-GPU berdasarkan PCIe disebut CrossFire. AMD dan NVIDIA telah merilis chipset motherboard yang mendukung sebanyak empat PCIe × 16 slot, yang memungkinkan konfigurasi kartu tri-GPU dan quad-GPU.

Ekstensi dan arah masa depan

Beberapa vendor menawarkan PCIe atas produk serat, tetapi ini umumnya menemukan gunakan hanya dalam kasus-kasus tertentu di mana PCIe transparan bridging adalah lebih baik untuk menggunakan standar yang lebih utama (seperti Infiniband atau Ethernet) yang mungkin memerlukan perangkat lunak tambahan untuk mendukungnya , implementasi saat ini fokus pada jarak daripada bandwidth mentah dan biasanya tidak menerapkan link penuh × 16.

Aplikasi pusat data tertentu (seperti cluster komputer besar) memerlukan penggunaan serat optik interkoneksi karena jarak dan keterbatasan latency yang melekat dalam kabel tembaga. Biasanya, standar-berorientasi jaringan seperti Ethernet atau Fibre Channel sudah cukup untuk aplikasi ini, tetapi dalam beberapa kasus

overhead diperkenalkan oleh protokol routable tidak diinginkan dan interkoneksi-tingkat yang lebih rendah, seperti InfiniBand, RapidIO, atau NUMAlink diperlukan. Standar lokal-bus seperti PCIe dan HyperTransport secara prinsip dapat digunakan untuk tujuan ini

namun pada 2012 ada vendor besar menawarkan sistem di pembuluh darah ini.

Thunderbolt dikembangkan oleh Intel sebagai antarmuka kecepatan tinggi untuk keperluan umum menggabungkan × 4 PCIe link dengan DisplayPort dan pada awalnya dimaksudkan untuk menjadi sebuah antarmuka serat semua, namun karena kesulitan awal dalam menciptakan serat interkoneksi ramah konsumen, implementasi yang paling awal adalah sistem-serat tembaga hibrida. Sebuah pengecualian, Sony VAIO Z VPC-Z2, menggunakan port USB tidak standar dengan komponen optik untuk menghubungkan ke layar adaptor PCIe tempel. Apple telah menjadi pendorong utama adopsi Thunderbolt sampai 2011, meskipun beberapa vendor lainnya

telah mengumumkan produk baru dan sistem menampilkan Thunderbolt.

Hardware ringkasan protokol

Link PCIe dibangun di sekitar pasangan searah berdedikasi serial (1-bit), koneksi point-to-point yang dikenal sebagai jalur. Hal ini kontras dengan koneksi PCI sebelumnya, yang merupakan sistem berbasis bus di mana semua perangkat berbagi sama bidirectional, 32-bit atau 64-bit paralel bus.

PCI Express adalah protokol berlapis, terdiri dari lapisan transaksi, lapisan data link, dan lapisan fisik. Data Link Layer dibagi untuk menyertakan kontrol akses (MAC) sublapisan media. Physical Layer dibagi menjadi sub-lapisan logis dan listrik. Fisik logis-sublayer berisi sublayer coding fisik (PCS). Istilah ini dipinjam dari IEEE 802 jaringan Model protokol.

Physical Layer

PCIe Physical Layer (PHY, PCIEPHY, PCI Express PHY, atau PCIe PHY) spesifikasi dibagi menjadi dua sub-lapisan, sesuai dengan spesifikasi listrik dan logis. Logis sublayer yang kadang-kadang lebih dibagi menjadi sublayer MAC dan PCS, walaupun pembagian ini tidak secara resmi bagian dari spesifikasi PCIe. Sebuah spesifikasi diterbitkan oleh Intel, Interface PHY untuk PCI Express (PIPA), mendefinisikan MAC / PCS partisi fungsional dan antarmuka antara dua sub-lapisan. Opium spesifikasi juga mengidentifikasi media lampiran (PMA) lapisan fisik, yang meliputi serializer / deserializer (SerDes) dan sirkuit analog lainnya, namun sejak SerDes implementasi sangat bervariasi antara vendor ASIC, PIPA tidak menentukan sebuah antarmuka antara PCS dan PMA .

Pada tingkat listrik, masing-masing terdiri dari dua jalur unidirectional LVDS atau PCML pasang di 2,525 Gbit / s. Mengirim dan menerima pasangan tersebut terpisah diferensial, untuk total empat kabel data yang per lajur.

Koneksi antara dua perangkat PCIe dikenal sebagai link, dan dibangun dari koleksi satu atau lebih jalur. Semua perangkat harus mendukung minimal satu jalur (× 1) link. Perangkat mungkin opsional link dukungan yang lebih luas terdiri dari 2, 4, 8, 12, 16, atau 32 jalur. Hal ini memungkinkan untuk kompatibilitas sangat baik dalam dua cara:

Sebuah kartu PCIe fisik cocok (dan bekerja dengan benar) pada slot yang setidaknya sebagai besar seperti itu (misalnya, kartu × 1 berukuran akan bekerja dalam ukuran slot);

Sebuah slot ukuran fisik yang besar (misalnya, × 16) dapat kabel elektrik dengan jalur sedikit (misalnya, × 1, × 4, 8 ×, atau 12 ×) asalkan menyediakan koneksi tanah yang dibutuhkan oleh slot fisik yang lebih besar ukuran.

Dalam kedua kasus, PCIe menegosiasikan tertinggi saling mendukung jumlah jalur. Banyak kartu grafis, motherboard dan versi bios diverifikasi untuk mendukung × 1, × 4, 8 × 16 × dan konektivitas pada koneksi yang sama.

Meskipun kedua akan sinyal-kompatibel, biasanya tidak mungkin untuk menempatkan kartu PCIe fisik lebih besar (misalnya, kartu × 16 ukuran) menjadi lebih kecil slot meskipun jika slot PCIe yang diubah atau riser yang digunakan kebanyakan motherboard akan membiarkan ini. Biasanya teknik ini digunakan untuk menampilkan ke beberapa monitor dalam konfigurasi simulator.

Lebar konektor PCIe adalah 8,8 mm, sedangkan tinggi adalah 11,25 mm, dan panjang adalah variabel. Bagian tetap konektor adalah 11,65 mm dan panjang berisi dua baris 11 (22 pin total), sedangkan panjang bagian lainnya adalah variabel tergantung pada jumlah jalur. Pin yang berjarak pada interval 1 mm, dan ketebalan kartu masuk ke konektor 1.8 mm

Transmisi data

PCIe mengirim semua pesan kontrol, termasuk interupsi, di link yang sama digunakan untuk data. Protokol serial yang tidak pernah akan diblokir, jadi latency masih sebanding dengan PCI konvensional, yang telah memotong jalur khusus.

Data yang ditransmisikan pada link beberapa jalur yang interleaved, yang berarti bahwa setiap byte diturunkan berturut-turut Lanes. Spesifikasi PCIe mengacu interleaving ini sebagai data striping. Sementara memerlukan kompleksitas hardware signifikan untuk menyinkronkan (atau deskew) yang masuk belang data, striping signifikan dapat mengurangi latency dari byte n pada link. Karena padding persyaratan, striping mungkin tidak selalu mengurangi latency paket data kecil pada link.

Seperti dengan data rate protokol transmisi serial tinggi lainnya, jam tertanam dalam sinyal. Pada tingkat fisik, PCI Express 2.0 menggunakan skema encoding 8B/10B

untuk memastikan bahwa string yang berturut-turut atau nol berturut-turut dibatasi panjangnya. Coding ini digunakan untuk mencegah penerima dari kehilangan melacak di mana tepi bit. Dalam skema pengkodean setiap delapan (uncoded) payload bit data akan diganti dengan 10 (encoded) bit dari data, menyebabkan 20% overhead listrik di bandwidth. Untuk meningkatkan bandwidth yang tersedia, PCI Express versi 3.0 menggunakan pengkodean 128b/130b gantinya: serupa tapi dengan overhead jauh lebih rendah.

Banyak protokol lain (seperti SONET) menggunakan bentuk yang berbeda encoding dikenal sebagai scrambling jam untuk menanamkan informasi ke dalam data stream. Spesifikasi PCIe juga mendefinisikan algoritma scrambling, tetapi digunakan untuk mengurangi interferensi elektromagnetik (EMI) dengan mencegah pola berulang data dalam aliran data yang ditransmisikan.

Data link layer

Data Link Layer melakukan tiga layanan penting untuk PCIe tautan mengungkapkan:

urutan transaksi lapisan paket (TLP) yang dihasilkan oleh lapisan transaksi,

memastikan pengiriman yang dapat diandalkan TLP antara dua endpoint melalui protokol pengakuan (ACK dan NAK sinyal) yang secara eksplisit mengharuskan replay diakui / buruk TLP,

menginisialisasi dan mengelola kredit kontrol aliran

Di sisi mengirimkan, lapisan data link menghasilkan urutan nomor incrementing untuk setiap TLP keluar. Ini berfungsi sebagai tag identifikasi unik untuk setiap TLP ditransmisikan, dan dimasukkan ke dalam header dari keluar TLP. A 32-bit kode cyclic redundancy check (dikenal dalam konteks ini sebagai link CRC atau LCRC) juga ditambahkan ke akhir setiap TLP keluar.

Di sisi receive, LCRC menerima TLP dan nomor urut keduanya divalidasi pada lapisan link. Jika salah satu cek LCRC gagal (menunjukkan kesalahan data), atau urutan-nomor di luar jangkauan (non-berturut-turut dari terakhir yang valid diterima TLP), maka buruk TLP, serta setiap TLP diterima setelah TLP buruk, dianggap tidak valid dan dibuang. Penerima mengirimkan pesan pengakuan negatif (NAK) dengan urutan-jumlah TLP valid, meminta kembali transmisi semua TLP maju itu urutan-nomor. Jika menerima TLP melewati pemeriksaan LCRC dan memiliki nomor urutan yang benar, itu dianggap sah. Kenaikan Link Penerima urutan-nomor (yang melacak terakhir diterima TLP baik), dan meneruskan TLP sah untuk transaksi lapisan penerima. Pesan ACK dikirim ke pemancar jarak jauh, yang menunjukkan TLP berhasil diterima (dan dengan perpanjangan, semua TLP dengan masa lalu-urutan nomor.)

Jika pemancar menerima pesan NAK, atau tidak ada pengakuan (NAK atau ACK) diterima sampai batas waktu berakhir, pemancar harus retransmit semua TLP yang tidak memiliki pengakuan positif (ACK). Cegah kerusakan terus-menerus dari perangkat atau media transmisi, link-layer menyajikan koneksi yang handal ke lapisan transaksi, karena protokol transmisi memastikan pengiriman TLP melalui media tidak dapat diandalkan.

Selain mengirim dan menerima TLP dihasilkan oleh lapisan transaksi, lapisan data-link juga menghasilkan dan mengkonsumsi DLLPs, data link lapisan paket. Nak ACK dan sinyal yang dikomunikasikan melalui DLLPs, seperti informasi kontrol aliran kredit, beberapa pesan manajemen daya dan arus informasi kredit kontrol (atas nama lapisan transaksi.)

Dalam prakteknya, jumlah in-flight, TLP diakui pada link dibatasi oleh dua faktor: ukuran buffer replay transmitter (yang harus menyimpan salinan semua TLP dikirimkan sampai penerima remote ACK mereka), dan kontrol aliran kredit yang dikeluarkan oleh penerima dengan pemancar. PCI Express mengharuskan semua penerima untuk mengeluarkan jumlah minimum kredit, untuk menjamin link memungkinkan pengiriman TLP PCIConfig dan TLP pesan.

Lapisan Transaksi

PCI Express menerapkan transaksi dibagi (transaksi dengan permintaan dan respon yang dipisahkan oleh waktu), memungkinkan link untuk membawa lalu lintas lainnya sementara target perangkat mengumpulkan data untuk tanggapan.

PCI Express menggunakan kontrol aliran berbasis kredit. Dalam skema ini, perangkat Advertises awal jumlah kredit untuk setiap buffer diterima dalam lapisan transaksinya. Perangkat di ujung link, bila mengirim transaksi ke perangkat ini, menghitung jumlah kredit masing-masing TLP mengkonsumsi dari rekeningnya. Perangkat pengirim hanya dapat mengirimkan TLP ketika hal tersebut tidak membuat hitungan kredit konsumsi yang melebihi batas kredit. Bila perangkat penerima selesai memproses TLP dari buffer, maka sinyal kembali kredit ke perangkat pengirim, yang meningkatkan batas kredit dengan jumlah yang dikembalikan. Counter kredit counter modular, dan perbandingan kredit untuk dikonsumsi batas kredit memerlukan aritmatika modular. Keuntungan dari skema ini (dibandingkan dengan metode lain seperti negara atau menunggu berbasis protokol transfer jabat tangan) adalah bahwa latency kredit kembali tidak mempengaruhi kinerja, asalkan batas kredit tidak ditemui. Asumsi ini biasanya bertemu jika setiap perangkat dirancang dengan ukuran yang cukup penyangga.

PCIe 1.x sering dikutip untuk mendukung data rate 250 MB / s di setiap arah, per jalur. Angka ini merupakan perhitungan dari fisik signaling menilai (2,5 Gbaud) dibagi dengan encoding overhead (10 bits per byte.) Ini berarti enambelas lane (× 16) PCIe kartu kemudian akan secara teoritis akan mampu 16 × 250 MB / s = 4 GB / s di setiap arah. Sementara ini benar dalam hal data byte, lebih bermakna perhitungan didasarkan pada data payload menilai, yang tergantung pada profil lalu lintas, yang merupakan fungsi dari tingkat tinggi aplikasi (software) dan protokol tingkat intermediate.

Seperti data rate serial sistem interkoneksi tinggi lainnya, PCIe memiliki protokol dan pengolahan overhead karena tambahan transfer kesegaran (CRC dan pengakuan). Panjang terus unidirectional transfer (seperti yang khas dalam pengontrol penyimpanan berkinerja tinggi) bisa mendekati> 95% dari baku (jalur) data rate PCIe. Ini transfer juga memperoleh keuntungan dari peningkatan jumlah Lanes (× 2, × 4, dll) Namun dalam aplikasi yang lebih khas (seperti USB atau Ethernet controller), lalu lintas adalah profil karakteristik sebagai data paket singkat dengan sering enforced Penghargaan

Jenis lalu lintas mengurangi efisiensi link, karena overhead dari paket parsing interrupts dan dipaksa (baik dalam perangkat antarmuka host atau PC CPU.) Menjadi protokol untuk perangkat yang terhubung ke papan sirkuit cetak yang sama, tidak memerlukan toleransi yang sama untuk transmisi kesalahan sebagai protokol untuk komunikasi jarak yang lebih jauh, dan dengan demikian, ini kehilangan efisiensi tidak khusus untuk PCIe.

Eksternal kartu PCIe

Secara teoritis, eksternal PCIe notebook dapat memberikan kekuatan grafis dari desktop, dengan menghubungkan notebook dengan kartu desktop video PCIe (terlampir dalam perumahan eksternal sendiri, dengan power supply yang kuat dan pendinginan), mungkin dengan sebuah antarmuka ExpressCard atau antarmuka Thunderbolt . Antarmuka ExpressCard menyediakan bit rate dari 5 Gbit / s (0,5 GB / s throughput yang), sedangkan antarmuka Thunderbolt menyediakan bit rate hingga 10 Gb / s (1 GB / s throughput yang). Namun, kartu video high-end bisa naik ke PCIe 3.0 × 16, yang dapat mentransfer pada 128 Gbit / s (15,75 GB / s), yang berarti transfer data ke kartu video eksternal dapat melakukan 10 kali lebih lambat daripada kartu video terhubung langsung ke motherboardIBM / Lenovo juga termasuk slot PCI-Express di Docking Station 250310U lanjutan mereka. Ini menyediakan slot berukuran setengah dengan × 16 soket panjang, tetapi hanya × 1 konektivitas.

Namun, stasiun docking dengan slot ekspansi menjadi kurang umum sebagai laptop mendapatkan kartu lebih maju video dan baik antarmuka DVI-D, atau DVI-D untuk melewati replikator pelabuhan dan stasiun docking.

Selain itu, Nvidia Quadro Plex telah mengembangkan eksternal PCIe video card yang dapat digunakan untuk aplikasi grafis canggih. Ini memerlukan kartu video PCI Express × 8 atau × 16 slot untuk kabel interkoneksi. [48] Pada tahun 2008, AMD mengumumkan ATI XGP teknologi, didasarkan pada sistem kabel milik yang kompatibel dengan PCIe × 8 transmisi sinyal.

Konektor ini tersedia di Fujitsu Amilo dan Acer Ferrari One notebook. Hanya Fujitsu memiliki kotak eksternal yang sebenarnya tersedia, yang juga bekerja pada Ferrari One. Baru-baru ini Acer meluncurkan dermaga grafis Dynavivid untuk XGP.

Sekarang ada kartu hubs dalam pembangunan yang satu dapat terhubung ke laptop melalui slot ExpressCard, meskipun mereka saat ini sedang langka, mengaburkan, atau tidak tersedia di pasar terbuka. Hub ini dapat menerima kartu berukuran penuh.

Magma dan ViDock juga menggunakan ExpressCard dan menerapkan penggunaan sistem grafis eksternal. ViDock besarbesaran casis ekspansi dirancang khusus untuk beradaptasi PCI Express kartu grafis untuk digunakan dengan ExpressCard dilengkapi komputer portabel. Hal ini memungkinkan menghubungkan kartu PCIe eksternal. Perkembangan teknologi ini masih berkembang, contoh lainnya adalah MSI GUS, Stasiun XG Asus.

Baru-baru ini, Intel dan Apple memperkenalkan Thunderbolt, memungkinkan untuk PCI (e) perangkat eksternal untuk mentransfer dua kali lipat kecepatan antarmuka ExpressCard. Namun kartu video eksternal mid-range masih akan sangat mencekik oleh koneksi yang lambat.

Thunderbolt telah memberikan kesempatan kepada produk-produk baru dan lebih cepat untuk berhubungan dengan kartu PCIe eksternal. Magma telah merilis 3T ExpressBox, yang dapat menampung hingga tiga kartu PCIe (dua pada 8 × dan satu di 4 ×), hal ini memungkinkan untuk workstation lebih baik ketika notebook tidak memiliki banyak port. MSI juga merilis Thunderbolt GUS II, chassis PCIe didedikasikan untuk produk cards.Other video seperti Soneta Echo Express dan mLink mLogic adalah Thunderbolt PCIe chassis dalam bentuk yang lebih kecil, ini memungkinkan konektivitas ke low-profile kartu video, kartu suara, kartu jaringan, memori, penyimpanan, dll